【導(dǎo)讀】復(fù)位信號(hào)是時(shí)序電路設(shè)計(jì)的基本信號(hào)���,本文描述了復(fù)位的定義���,分類及不同復(fù)位設(shè)計(jì)的影響���,并討論了針對(duì)FPGA和CPLD的內(nèi)部自復(fù)位方案。

1���、定義

復(fù)位信號(hào)是一個(gè)脈沖信號(hào)���,它會(huì)使設(shè)計(jì)的電路進(jìn)入設(shè)定的初始化狀態(tài),一般它作用于寄存器���,使寄存器初始化為設(shè)定值���;其脈沖有效時(shí)間長(zhǎng)度必須大于信號(hào)到達(dá)寄存器的最大時(shí)延,這樣才有可能保證復(fù)位的可靠性���。

下面將討論FPGA/CPLD的復(fù)位電路設(shè)計(jì)���。

2、分類及不同復(fù)位設(shè)計(jì)的影響

根據(jù)電路設(shè)計(jì)���,復(fù)位可分為異步復(fù)位和同步復(fù)位���。

對(duì)于異步復(fù)位,電路對(duì)復(fù)位信號(hào)是電平敏感的���,如果復(fù)位信號(hào)受到干擾���,如出現(xiàn)短暫的脈沖跳變���,電路就會(huì)部分或全部被恢復(fù)為初始狀態(tài),這是我們不愿看到的���。因此���,異步復(fù)位信號(hào)是一個(gè)關(guān)鍵信號(hào),在電路設(shè)計(jì)時(shí)���,如PCB Layout需要對(duì)其優(yōu)先考慮和作特別保護(hù)���,避免信號(hào)線出現(xiàn)的干擾產(chǎn)生非期望的復(fù)位。

對(duì)于同步復(fù)位���,電路在時(shí)鐘信號(hào)下對(duì)復(fù)位信號(hào)進(jìn)行采樣���,復(fù)位信號(hào)只在時(shí)鐘的跳變沿(邊沿)有效;如果復(fù)位信號(hào)受到干擾,只要該干擾脈沖不出現(xiàn)在時(shí)鐘的跳變沿���,或者脈沖能量不足以使時(shí)鐘采樣到有效的信號(hào),電路就不會(huì)被異常復(fù)位���,這樣可有效降低信號(hào)線上出現(xiàn)毛刺等干擾信號(hào)所產(chǎn)生誤復(fù)位操作的概率���,提高了電路的抗干擾能力。

在FPGA/CPLD設(shè)計(jì)中���,如果復(fù)位信號(hào)是通過組合邏輯產(chǎn)生的���,我們?cè)诜抡娴臅r(shí)候經(jīng)常可以看到���,由于組合邏輯的競(jìng)爭(zhēng)冒險(xiǎn)產(chǎn)生的毛刺���,會(huì)導(dǎo)致采用異步復(fù)位設(shè)計(jì)的電路被誤復(fù)位;因此在設(shè)計(jì)當(dāng)中要對(duì)異步復(fù)位信號(hào)進(jìn)行同步化處理���,避免誤操作產(chǎn)生���。

具體的做法是:設(shè)計(jì)一個(gè)專門的復(fù)位模塊���,它對(duì)復(fù)位信號(hào)(記為R)進(jìn)行同步化處理,產(chǎn)生新的復(fù)位信號(hào)(記為RS)���,這個(gè)RS信號(hào)可作為其他模塊的復(fù)位輸入信號(hào)���;而其他模塊的電路可全部采用異步復(fù)位的設(shè)計(jì)方式;這樣的設(shè)計(jì)對(duì)復(fù)位信號(hào)進(jìn)行統(tǒng)一處理���,可根據(jù)需要調(diào)整���,相對(duì)靈活,需要注意的是���,要盡量降低時(shí)鐘邊沿與復(fù)位信號(hào)R失效時(shí)刻的亞穩(wěn)態(tài)出現(xiàn)概率���。

在實(shí)際的FPGA/CPLD應(yīng)用當(dāng)中,會(huì)出現(xiàn)沒有外部復(fù)位信號(hào)的情景���,而FPGA/CPLD的時(shí)序設(shè)計(jì)又需要一個(gè)復(fù)位信號(hào)來使內(nèi)部的寄存器初始化為設(shè)定的狀態(tài)���,這時(shí)候就需要通過內(nèi)部邏輯產(chǎn)生一個(gè)內(nèi)部復(fù)位信號(hào)���。

3、FPGA內(nèi)部自復(fù)位方法

內(nèi)部自復(fù)位信號(hào)是器件上電后僅產(chǎn)生一次的信號(hào)���,之后一直保持無效至器件掉電。這種一次性信號(hào)���,產(chǎn)生它的數(shù)字電路自身需要一個(gè)初始的確定狀態(tài)���,并且需要上電后就處于該種狀態(tài);對(duì)于FPGA來說���,其內(nèi)部寄存器在上電后的狀態(tài)是不確定的���,即無法預(yù)期的,因此利用寄存器的狀態(tài)來產(chǎn)生復(fù)位信號(hào)���,不是那么可靠���;但我們可以考慮FPGA的其他資源���,一般FPGA內(nèi)部都有RAM資源,這些RAM都可以被配置數(shù)據(jù)初始化的���,也就是說當(dāng)FPGA上電配置完成后���,被初始化的RAM的數(shù)據(jù)內(nèi)容是確定的。利用這個(gè)特點(diǎn)���,我們就可以設(shè)計(jì)可靠的內(nèi)部自復(fù)位信號(hào)���。

下面給出實(shí)現(xiàn)方法:

1)配置一個(gè)數(shù)據(jù)長(zhǎng)度為1位,地址長(zhǎng)度為n位���,且全部初始化為1的單口RAM���;

2)設(shè)計(jì)一個(gè)針對(duì)該單口RAM的讀寫模塊,其內(nèi)部維護(hù)一個(gè)n位讀指針rp和一個(gè)n位寫指針wp���,rp在每個(gè)時(shí)鐘節(jié)拍將其值賦給wp后并加1���,保證rp領(lǐng)先于wp���,將單口RAM的輸出數(shù)據(jù)作為復(fù)位信號(hào),另外RAM的輸入數(shù)據(jù)固定為0���;這樣RAM數(shù)據(jù)被先讀出���,然后被置為0,因此上電配置完成后經(jīng)過2n個(gè)時(shí)鐘節(jié)拍���,RAM的數(shù)據(jù)從全1變成全0���,從而實(shí)現(xiàn)一次性脈沖信號(hào)的產(chǎn)生���。另外���,通過控制地址長(zhǎng)度n或時(shí)鐘頻率,就可得到所需的脈沖寬度���。

4���、CPLD內(nèi)部自復(fù)位方法

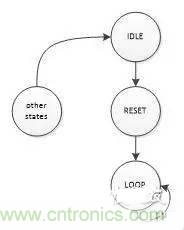

CPLD其內(nèi)部沒有RAM���,這樣就不能依靠RAM的初始化數(shù)據(jù)來產(chǎn)生可靠的復(fù)位;從原理上說���,器件上電后���,其寄存器的狀態(tài)是不確定的,因此我們是沒法得到一個(gè)確定的初始狀態(tài)去產(chǎn)生一個(gè)可靠的內(nèi)部復(fù)位信號(hào)���,不過我們還是可以產(chǎn)生一個(gè)有一定失敗概率但概率可控的復(fù)位信號(hào)���,其基本原理是:設(shè)計(jì)一個(gè)n位的狀態(tài)機(jī),見下圖���,其中一種狀態(tài)表示復(fù)位結(jié)束(記為L(zhǎng)OOP)���,只要進(jìn)入該狀態(tài)就會(huì)一直保持在LOOP狀態(tài)上,至于其他狀態(tài)都會(huì)跳入復(fù)位狀態(tài)(記為RESET)���,RESET狀態(tài)是暫態(tài)���,一個(gè)時(shí)鐘周期就離開進(jìn)入LOOP狀態(tài)���;由于狀態(tài)LOOP出現(xiàn)的概率僅為:1/2n,我們控制n的長(zhǎng)度���,就可以將復(fù)位失敗概率控制在設(shè)定的要求內(nèi)���。

Figure 1 內(nèi)部復(fù)位狀態(tài)圖

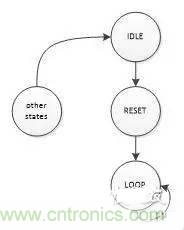

在實(shí)際的應(yīng)用中,我們發(fā)現(xiàn)某些CPLD產(chǎn)品有一個(gè)特性���,見下圖:

Figure 2 摘自某產(chǎn)品的《handbook.pdf》

從上圖可知���,該CPLD在完成內(nèi)部配置后,其內(nèi)部所有寄存器都處于清零狀態(tài)���,因此可以說寄存器在上電后是有一個(gè)確定的初始狀態(tài),但這個(gè)特性應(yīng)該是對(duì)通過修改具有固定內(nèi)連電路的邏輯功能來編程的CPLD所特有的���,對(duì)通過改變內(nèi)部連線的布線來編程的FPGA來說���,并未查到它具有這種特性,因此我們可以采取更簡(jiǎn)單的方法來產(chǎn)生內(nèi)部自復(fù)位信號(hào):維護(hù)一個(gè)n位計(jì)數(shù)器���,它隨時(shí)鐘節(jié)拍一直遞增直至某個(gè)設(shè)定的最大值M���,之后就停止計(jì)數(shù)���,這樣M之前的狀態(tài)就可實(shí)現(xiàn)為一個(gè)一次性的脈沖信號(hào)。

另外���,該產(chǎn)品用戶如果希望配置完成后CPLD內(nèi)部各個(gè)寄存器的狀態(tài)處于可控或者特定的狀態(tài)(尤其當(dāng)其值不一定是清零的狀態(tài))���,那么用戶可以使用器件提供的專用管腳DEV_CLRn來達(dá)到所期望的效果。

5���、結(jié)語(yǔ)

復(fù)位信號(hào)是時(shí)序電路設(shè)計(jì)的基本信號(hào)���,雖然只是一個(gè)脈沖信號(hào),但要使設(shè)計(jì)的電路可靠地工作���,復(fù)位信號(hào)也是一個(gè)需認(rèn)真對(duì)待的因素���。