【導讀】從98年底進入PCB設(shè)計相關(guān)行業(yè)到現(xiàn)在已有18年,遺憾的是至今還沒見過PCB設(shè)計行業(yè)內(nèi)高人關(guān)于PCB軟件發(fā)展方向及職業(yè)發(fā)展方向指引的預測文章。由于一直在一線PCB設(shè)計相關(guān)的行業(yè)中游走,經(jīng)歷的這些年對這個行業(yè)的發(fā)展有了些個人的體會,把這個體會再說大一點就改成“發(fā)展方向預測”。這些膚淺的預測分享希望能為在這個苦逼行業(yè)的從業(yè)人員提供一些有價值的職業(yè)方向參考。

業(yè)界很多大牛,但都比較低調(diào)沒人愿意寫這些東西,因此我先跳出來,等后面的人補刀。

預測

前段參加了2016 cadence技術(shù)巡回展,發(fā)現(xiàn)其中的內(nèi)容基本是軟件在某些功能上的效率提高及各模塊間的融合,種種跡象更堅定了我的預測方向。

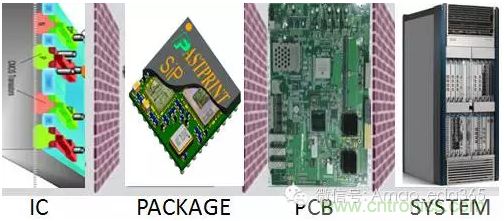

預測1:IC封裝設(shè)計功能與PCB設(shè)計功能將進一步融合,使IC到PCB的CO-DESIGN更通暢。

國家在IC及封裝制造業(yè)實質(zhì)性的大投入在最近幾年,發(fā)生在2015年間IC相關(guān)的上下游公司大手筆行業(yè)并購就可以略見一斑,況且這種并購還沒發(fā)現(xiàn)有減緩的跡象,這些也是國家的大戰(zhàn)略方向,因此以后的10年是國內(nèi)IC行業(yè)大發(fā)展的10年。

IC封裝領(lǐng)域也需跟進,體現(xiàn)在聯(lián)系IC產(chǎn)業(yè)與PCB產(chǎn)業(yè)的橋梁---IC封裝設(shè)計軟件及相應(yīng)的封裝加工制造行業(yè)。這也能說明IC封裝設(shè)計軟件會是EDA軟件的重點發(fā)展方向。

當年剛進入華為時主要是從事PCB設(shè)計,那時在PCB行業(yè)從高速概念的引進到仿真等方面的普及再到現(xiàn)在中國PCB DESIGN HOUSE的成長(PCB DESIGN HOUSE實則為國內(nèi)行業(yè)培養(yǎng)了大批的高速PCB設(shè)計人才),這些事實促使國內(nèi)高速PCB設(shè)計的迅速普及國內(nèi)PCB制造行業(yè)在加工及材料方面的的提升也用了近10多年的時間。國內(nèi)高速PCB設(shè)計成長過程可以閱讀《華為研發(fā)14載-那些一起奮斗過的互連歲月》,這本書中所描述的故事基本可以看成是中國高速PCB設(shè)計成長的縮影。

現(xiàn)在各EDA軟件商主推的IC TO PCB CO-DESIGN功能,雖然在流程上基本可以實現(xiàn),但是畢竟IC設(shè)計與IC PACKAGE/PCB設(shè)計等不在一個平臺上,在SI/PI/THERMAL/STRESS等仿真時的數(shù)據(jù)交換,目前還不是很完美及高效。另一個問題是國內(nèi)公司目前能設(shè)計稍復雜些IC的公司真沒有幾家,絕大多數(shù)設(shè)計的IC規(guī)模都比較小---也就100-200個管腳,設(shè)計起來不太復雜,這類規(guī)模的IC設(shè)計使用CO-DESIGN流程簡直就是殺雞使用了牛刀,IC封裝的管腳沒有上千時根本就不知道CO-DESIGN流程的重要性,因而往往連需求也提不出來。這些大規(guī)模的IC設(shè)計也將在此后的10年內(nèi)快速增長。

IC封裝設(shè)計方面的書籍,目前行業(yè)內(nèi)非常少,對于初入門者可以參考《IC封裝基礎(chǔ)與工程設(shè)計實例》,因為它從封裝基礎(chǔ)知識、設(shè)計、加工,生產(chǎn)等各方面作了較為系統(tǒng)性的論述。

預測2:EDA軟件的功能模塊更加完善、功能更強大及更系統(tǒng)化

IC封裝設(shè)計與PCB設(shè)計雖表面看起來類似,但區(qū)別還是挺大,因為IC封裝設(shè)計方案時還需要考慮SI/PI/EMC/3D仿真/熱/應(yīng)力/成本/可加工性等諸多問題,因此現(xiàn)有EDA廠商中缺少相應(yīng)模塊的還需要補齊,如缺少熱或應(yīng)力仿真模塊時要補上才使本軟件更具競爭力,更方便用戶封裝設(shè)計時進行方案評估及詳細設(shè)計。

預測3:對軟件的現(xiàn)有功能進行UPDATE使效率更高及引入一些新的Features

不同的EDA軟件間相互借鑒,最后所有EDA軟件在單個PCB設(shè)計軟件功能會基本類同。如:

1)多人協(xié)同并行設(shè)計的方法,現(xiàn)在都有核心算法避過對方專利實現(xiàn)實時同步設(shè)計功能。

2)經(jīng)典的三維電磁場仿真工具初衷不是用在PCB上,只是后來這方面的需求多了才加強了這方面的功能及算法,PCB設(shè)計軟件最后也會加強在三維電磁場方面的能力,同時利用自身的PCB設(shè)計軟件平臺會使設(shè)計門檻變低,數(shù)據(jù)在自身后臺傳遞效率更高。

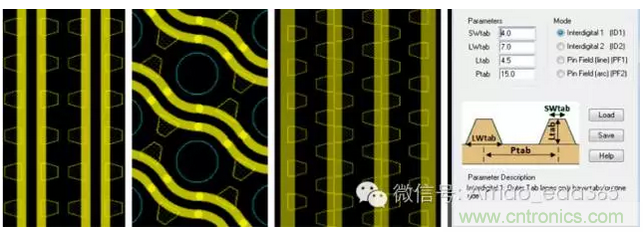

3)再如對于DDR4的布線處理方面效率軟件功能模塊的更新會使操作越來越方便。

PCB設(shè)計行業(yè)人員的就業(yè)機會

從IC LAYOUT->BUFFER SELECTION->IC PACKAGE DESIGN-> PCB DESIGN,這條鏈路上都都很精通的人到目前為止我還不曾遇到過,畢竟學業(yè)有專攻,個人的精力也有限。但是上面鏈路中從BUFFER SELECTION->IC PACKAGE DESIGN-> PCB DESIGN這些由于與SI及PCB設(shè)計相關(guān),還是有機會都掌握。這個流程中PCB設(shè)計從業(yè)人員可以提升IC Package Design、Si、PI、Thermal Simulation、Stress、Manufacture、Script Language等方面的知識,學好這些相關(guān)的知識也可以是另一個職業(yè)的途徑。

如看好國內(nèi)IC行業(yè)的今后10年的發(fā)展,對應(yīng)的IC PACKAGE也有較好的機會。當然個別有能耐的同學以后不走技術(shù)路線,也就不需要考慮我提到的技術(shù)點了。

最后,PCB設(shè)計從業(yè)者需對自身有信心,面對幾萬個PIN的PCB布線上都有的那分耐心,沒有你達不成的目標!------PCB設(shè)計,不僅僅是眼前“飛線”的拉扯!

希望大家有不同意見跟貼發(fā)表評論及補刀,我后面持續(xù)跟進及修正觀點。