【導(dǎo)讀】在處理電路板布局和器件封裝產(chǎn)生的寄生電感時(shí),快速開(kāi)關(guān)器件接通和關(guān)斷控制是關(guān)鍵問(wèn)題。本文英飛凌專(zhuān)家分析了快速開(kāi)關(guān)MOSFET封裝寄生電感對(duì)開(kāi)關(guān)性能的影響。封裝源電感是決定切換時(shí)間的關(guān)鍵參數(shù),后者與開(kāi)關(guān)速度和開(kāi)關(guān)可控性密切相關(guān)。

高效率已成為開(kāi)關(guān)電源(SMPS)設(shè)計(jì)的必需要求。為了達(dá)成這一要求,越來(lái)越多許多功率半導(dǎo)體研究人員開(kāi)發(fā)了快速開(kāi)關(guān)器件,舉例來(lái)說(shuō),降低器件的寄生電容,并實(shí)現(xiàn)低導(dǎo)通電阻,以降低開(kāi)關(guān)損耗和導(dǎo)通損耗。這些快速開(kāi)關(guān)器件容易觸發(fā)開(kāi)關(guān)瞬態(tài)過(guò)沖。這對(duì)SMPS設(shè)計(jì)中電路板布局帶來(lái)了困難,并且容易引起了柵極信號(hào)振蕩。為了克服開(kāi)關(guān)瞬態(tài)過(guò)沖,設(shè)計(jì)人員通常采取的做法是借助緩沖電路提高柵極電阻阻值,以減慢器件開(kāi)關(guān)速度,抑制過(guò)沖,但這會(huì)造成相對(duì)較高的開(kāi)關(guān)損耗。對(duì)于采用標(biāo)準(zhǔn)通孔封裝的快速開(kāi)關(guān)器件,總是存在效率與易用性的折衷問(wèn)題。

在處理電路板布局和器件封裝產(chǎn)生的寄生電感時(shí),快速開(kāi)關(guān)器件接通和關(guān)斷控制是關(guān)鍵問(wèn)題。 特別是,封裝源極寄生電感是是器件控制的關(guān)鍵因素。在本文中,英飛凌提出了一種用于快速開(kāi)關(guān)超結(jié)MOSFET的最新推出的TO247 4引腳器件封裝解決方案。這個(gè)解決方案將源極連接分為兩個(gè)電流路徑;一個(gè)用于實(shí)現(xiàn)功率連接,另一個(gè)用于實(shí)現(xiàn)驅(qū)動(dòng)器連接。這樣一來(lái),器件就能保持快的開(kāi)關(guān)速度,同時(shí)又不必犧牲接通和關(guān)斷控制能力。

本文編排如下:在第二節(jié),將利用硬開(kāi)關(guān)升壓轉(zhuǎn)換器來(lái)分析并開(kāi)發(fā)一個(gè)簡(jiǎn)單的高頻模型,該模型采用了具備MOSFET寄生參數(shù)和電路板寄生參數(shù)的標(biāo)準(zhǔn)通孔封裝傳統(tǒng)的TO247(即:電源電流路徑和驅(qū)動(dòng)電流路徑是相同的)。第三節(jié)將對(duì)最新推出的TO247 4引腳封裝做詳盡的電路分析,以表明TO247 4引腳封裝在開(kāi)關(guān)速度、效率和驅(qū)動(dòng)能力等方面的有效性。最后,第四節(jié)分析了實(shí)驗(yàn)波形和效率測(cè)量,以驗(yàn)證最新推出的TO247 4引腳封裝的性能。

II.分析升壓轉(zhuǎn)換器中采用傳統(tǒng)的TO247封裝的MOSFET

A.開(kāi)關(guān)瞬態(tài)下的MOSFET操作時(shí)序

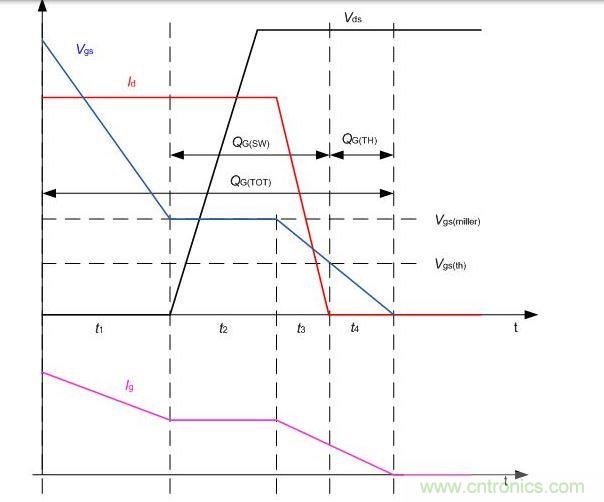

要分析快速開(kāi)關(guān)MOSFET中的封裝寄生電感產(chǎn)生的影響,必須十分理解MOSFET工作處理。硬開(kāi)關(guān)關(guān)斷通常出現(xiàn)在硬開(kāi)關(guān)拓?fù)浜土汶妷洪_(kāi)關(guān)拓?fù)渲?。本小?jié)將逐步分析MOSFET關(guān)斷瞬態(tài)操作。圖1所示為硬開(kāi)關(guān)關(guān)斷瞬態(tài)下,理想MOSFET的工作波形和工作順序。

圖1 升壓轉(zhuǎn)換器中的MOSFET的典型關(guān)斷瞬態(tài)波形

當(dāng)驅(qū)動(dòng)器發(fā)出關(guān)斷信號(hào)后,即開(kāi)始階段1 [t=t1]操作,柵極與源極之間的MOSFET電容器Cgs將開(kāi)始放電。此時(shí),MOSFET阻斷特性保持不變。這個(gè)t1階段被稱為延時(shí),它表征著MOSFET的響應(yīng)時(shí)間。當(dāng)MOSFET柵源電壓Vgs達(dá)到柵極平臺(tái)電壓Vgs(Miller)時(shí),這個(gè)階段便告結(jié)束。

[page]

當(dāng)Vgs與Vgs(Miller) 相等之后,將進(jìn)入階段2 [t=t2],在此期間,其電壓水平將保持不變。負(fù)載電流將對(duì)漏極與源極之間的MOSFET電容器Cds進(jìn)行充電,以重建空間電荷區(qū)。這個(gè)階段將一直持續(xù)至MOSFET漏源電壓Vds達(dá)到電路輸出電壓時(shí)為止。

階段3 [t=t3] ,Cgs將繼續(xù)放電。漏電流Id和Vgs開(kāi)始線性下降,阻斷MOSFET導(dǎo)通通道。當(dāng)Vgs 與柵極閾值電壓Vgs(th)相等,并且Id變?yōu)榱銜r(shí),這個(gè)階段即結(jié)束。這個(gè)階段結(jié)束后,MOSFET將完全關(guān)斷。

階段4 [t=t4] ,柵極驅(qū)動(dòng)對(duì)Cgs持續(xù)放電,直至Vgs電壓水平變?yōu)榱恪?/div>

B.傳統(tǒng)的TO247封裝MOSFET的開(kāi)關(guān)瞬態(tài)特性分析

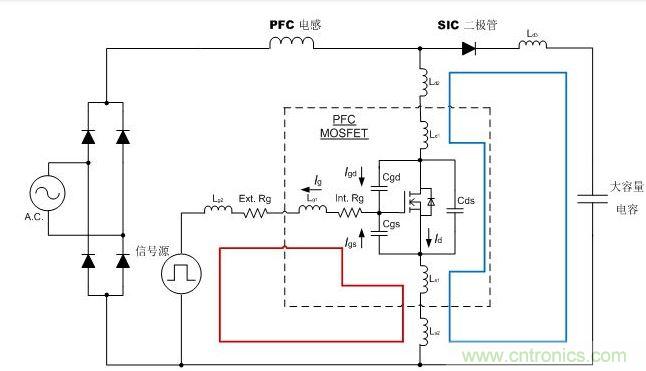

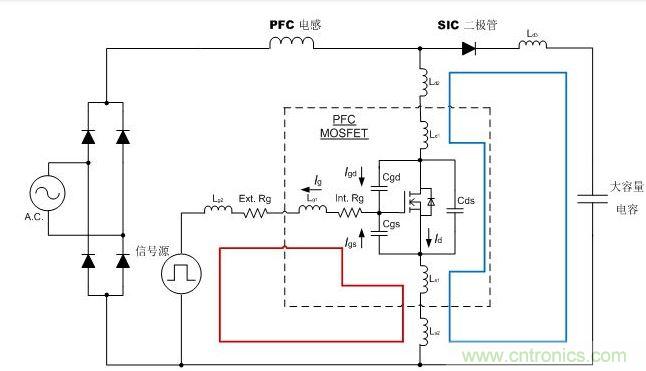

利用升壓轉(zhuǎn)換器,評(píng)估了封裝寄生電感對(duì)MOSFET開(kāi)關(guān)特性的影響。圖2所示為傳統(tǒng)的TO247 MOSFET等效模型的詳情,以及升壓轉(zhuǎn)換器電路和寄生電感的詳情。對(duì)于MOSFET模型, 3個(gè)電容為硅結(jié)構(gòu),分別位于各個(gè)連接引腳之間:柵漏電容Cgd、漏源電容Cds和柵源電容Cgs。鍵合絲產(chǎn)生了MOSFET寄生電感:柵極寄生電感Lg1、漏極寄生電感Ld1和源極寄生電感Ls1。這個(gè)模型也包含了電路板電路布局產(chǎn)生的雜散電感:Ld2、Ld3、Lg2和Ls2。分析中,LS等于Ls1+Ls2,Lg等于Lg1+Lg2,RG等于Int.Rg+Ext.Rg。

圖2. 升壓轉(zhuǎn)換器中的TO247封裝MOSFET等效模型和寄生電感

參照小節(jié)A中討論的關(guān)斷瞬態(tài)順序,源極電感LS主要在瞬態(tài)階段3影響到MOSFET開(kāi)關(guān)特性。柵極驅(qū)動(dòng)路徑顯示為紅色,漏電流在藍(lán)色環(huán)路上流動(dòng)。快速電流瞬態(tài)過(guò)程中,LS 引發(fā)電壓降VLs,這能抵消會(huì)降低驅(qū)動(dòng)能力和減慢器件速度的柵極電壓。

通過(guò)在驅(qū)動(dòng)環(huán)路上運(yùn)用基爾霍夫電壓定律,柵源電壓Vgs(t)可以表示為:

從等式(2)和(3)可知,源極電感可以減慢開(kāi)關(guān)瞬態(tài),加劇開(kāi)關(guān)過(guò)程中的有關(guān)能耗。在傳統(tǒng)的TO247 MOSFET配置中,電路源極電感是MOSFET封裝源電感Ls1與電路板布局源極電感Ls2之和。始終必須最大限度地降低封裝源和電路板寄生的源極電感,因?yàn)槎呔鶠殛P(guān)鍵控制要素。 較之采用通孔封裝的MOSFET,通過(guò)將無(wú)引線SMD封裝用于MOSFET,可以最大限度地降低封裝中的寄生源電感。 因此,采用SMD封裝的MOSFET也能實(shí)現(xiàn)快速開(kāi)關(guān),同時(shí)降低開(kāi)關(guān)損耗。適用于4引腳器件的SMD封裝名為“ThinkPAK 8X8”。

[page]

III.分析升壓轉(zhuǎn)換器中采用最新推出的TO247 4引腳封裝的MOSFET

英飛凌已經(jīng)在CoolMOS系列器件中推出新的封裝概念“4引線封裝”,其中,通孔封裝名為“TO-247 4PIN”。如圖3中的虛線框內(nèi)所示,最新推出的TO-247 4引腳模型提供了一個(gè)額外的源極連接引腳。在內(nèi)部連接中,引腳分離始于芯片內(nèi)部,充當(dāng)開(kāi)爾文源。電源引腳“S”為電源接地提供了連接。開(kāi)爾文源引腳,源-感側(cè)引腳“SS”直接連接至驅(qū)動(dòng)器地線,以便將驅(qū)動(dòng)電流與電源電流路徑分離。

由于源極分離,瞬態(tài)過(guò)程中源極電感對(duì)柵極驅(qū)動(dòng)電路的影響將被消除。參見(jiàn)圖3,驅(qū)動(dòng)環(huán)路顯示為紅色,漏極電流環(huán)路不再相互作用。源電感引起的壓降不再影響柵源電壓Vgs(t)。如第二節(jié)中所討論,階段3時(shí)的柵源電壓Vgs(t)為

圖3. 升壓轉(zhuǎn)換器中的TO247 4引腳封裝MOSFET等效模型

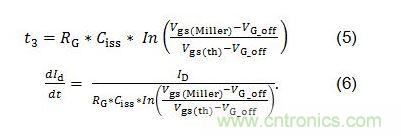

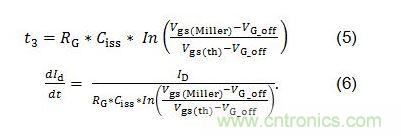

對(duì)應(yīng)的時(shí)間段t3和漏極電流變化速率dId/dt可表示為:

從等式(5)和(6)可知,影響MOSFET電流速率的源極引腳電感被消除了。根據(jù)等式(2)和(5),較之TO247封裝MOSFET,這縮短了器件的開(kāi)關(guān)速度,降低了開(kāi)關(guān)損耗。最新推出的TO247 4引腳MOSFET可實(shí)現(xiàn)相對(duì)較快的開(kāi)關(guān)動(dòng)作,從而降低開(kāi)關(guān)損耗。

[page]

IV.實(shí)驗(yàn)驗(yàn)證

A.實(shí)驗(yàn)測(cè)試波形

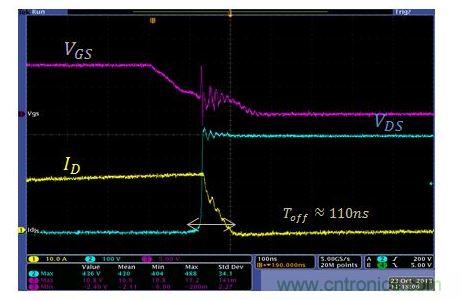

將升壓PFC轉(zhuǎn)換器用作測(cè)量平臺(tái),進(jìn)行評(píng)估。傳統(tǒng)的TO247封裝MOSFET和最新推出的TO247 4引腳封裝MOSFET將被用作平臺(tái)主用開(kāi)關(guān)器件,以驗(yàn)證最新推出的TO247 4引腳封裝MOSFET優(yōu)于傳統(tǒng)的TO247封裝的開(kāi)關(guān)性能和柵極控制能力。

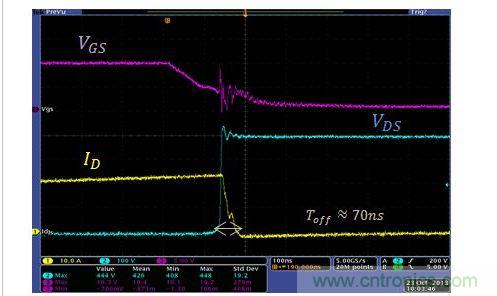

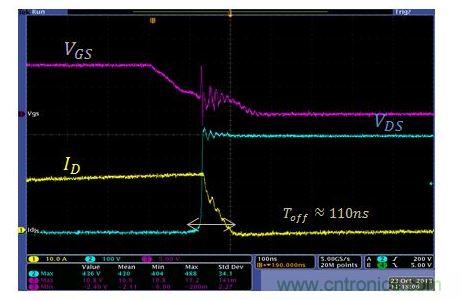

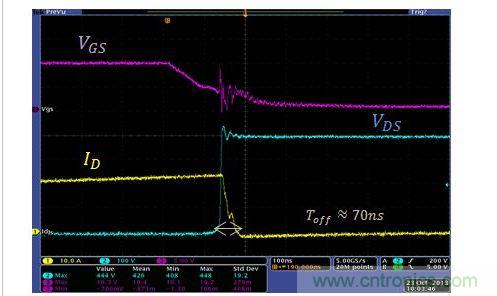

圖4所示為傳統(tǒng)的TO247封裝(上)和最新推出的TO247 4引腳封裝(下)的硬開(kāi)關(guān)關(guān)斷波形對(duì)比。根據(jù)測(cè)得波形,從Vds(t)(藍(lán)色波形)到Id(t) (黃色波形)的TO247 4引腳封裝MOSFET的穿過(guò)時(shí)間,比最新推出的TO247封裝MOSFET縮短了約40%。Vds 與ID 的重疊越少,意味著開(kāi)關(guān)損耗越低。較之于傳統(tǒng)的TO247封裝,最新推出的TO247 4引腳封裝MOSFET的振蕩幅度Vgs (t) (紫色波形)也降低了30%。因此,最新推出的TO247 4引腳封裝提供了更加可靠的開(kāi)關(guān)控制。

圖4. TO247封裝MOSFET(上)和TO247 4引腳封裝MOSFET(下)的MOSFET關(guān)斷瞬態(tài)波形。試驗(yàn)條件:Ext. Rg=5 Ω,12 V柵極驅(qū)動(dòng)電壓、試驗(yàn)器件IPZ65R019C7

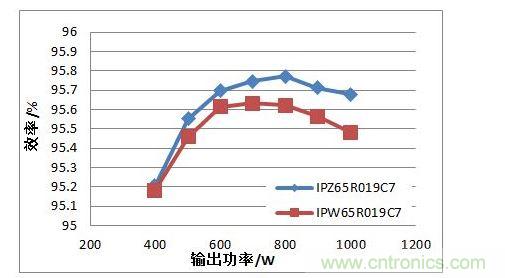

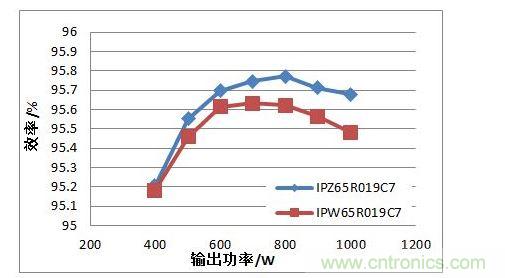

最新推出的TO247 4引腳封裝MOSFET切換時(shí)間,比傳統(tǒng)的TO247封裝短。得益于開(kāi)關(guān)損耗降低,最新推出的TO247 4引腳封裝MOSFET實(shí)現(xiàn)了更高效率,如圖5所示。在輸入電壓為110 Vac的滿負(fù)荷試驗(yàn)條件下,相比于傳統(tǒng)的TO247封裝的試驗(yàn)結(jié)果,最新推出的TO247 4引腳封裝MOSFET的效率提高了0.2%。在高電壓情況下,即當(dāng)輸入電壓為220 Vac時(shí),也實(shí)現(xiàn)了與之一致的效率提升。

圖5. 在110 Vac 輸入電壓條件下,TO247 4引腳封裝MOSFET與TO247封裝MOSFET的PFC效率對(duì)比。測(cè)試條件:Ext. Rg=5 Ω,開(kāi)關(guān)頻率=100 kHz,測(cè)試器件:具備相同硅芯片的IPW65R019C7(TO247)和IPZ65R019C7(TO247 4引腳)

V.結(jié)語(yǔ)

本文分析了快速開(kāi)關(guān)MOSFET封裝寄生電感對(duì)開(kāi)關(guān)性能的影響。封裝源電感是決定切換時(shí)間的關(guān)鍵參數(shù),后者與開(kāi)關(guān)速度和開(kāi)關(guān)可控性密切相關(guān)。英飛凌最新推出的TO247 4引腳封裝MOSFET能最大限度地減少傳統(tǒng)的TO247封裝寄生電感造成的不利影響,實(shí)現(xiàn)更高系統(tǒng)效率。