【導(dǎo)讀】低壓差(LDO)調(diào)節(jié)器,或者說任何電路的噪聲源都可以分為兩大類:內(nèi)部噪聲和外部噪聲。內(nèi)部噪聲好比是您頭腦中的噪聲,外部噪聲則好比是來自噴氣式飛機(jī)的噪聲。

為什么噪聲源很重要

噪聲重要與否,取決于它對目標(biāo)電路工作的影響程度。例如,一個(gè)開關(guān)電源在3 MHz時(shí)具有顯著的輸出電壓紋波,如果它為之供電的電路僅有幾Hz的帶寬,如溫度傳感器等,則該紋波可能不會產(chǎn)生任何影響。但是,如果該開關(guān)電源為RF鎖相環(huán)(PLL)供電,結(jié)果可能大不相同。

為了成功設(shè)計(jì)一個(gè)魯棒的系統(tǒng),了解噪聲源、其頻譜特性、降噪策略以及目標(biāo)電路對該噪聲的敏感程度至關(guān)重要。

本應(yīng)用筆記還會力圖澄清電源抑制比(PSRR)與內(nèi)生噪聲的區(qū)別,并且說明如何應(yīng)用數(shù)據(jù)手冊中每個(gè)參數(shù)的規(guī)格。

噪聲源

低壓差(LDO)調(diào)節(jié)器,或者說任何電路的噪聲源都可以分為兩大類:內(nèi)部噪聲和外部噪聲。內(nèi)部噪聲好比是您頭腦中的噪聲,外部噪聲則好比是來自噴氣式飛機(jī)的噪聲。

對于電子電路,內(nèi)部噪聲是指任何電子器件內(nèi)部產(chǎn)生的噪聲,外部噪聲則是指從電路外部傳到電路中的噪聲。

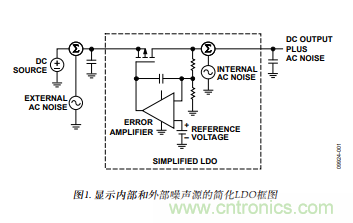

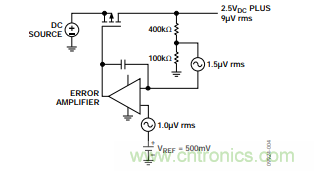

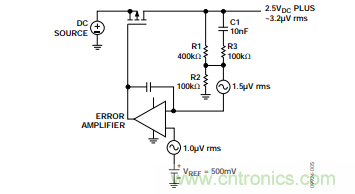

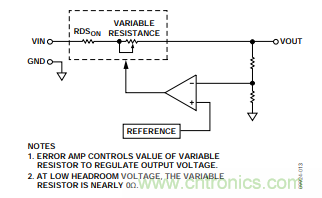

LDO易于使用,但PSRR和內(nèi)生噪聲常常令人困惑。許多情況下,都將二者一起簡單地歸類為噪聲,這是對性能指標(biāo)的誤用,因?yàn)檫@兩種噪聲具有不同的特性,并且用于降低其對系統(tǒng)性能影響的方法也不同。圖1為LDO的簡單框圖,顯示了內(nèi)部噪聲源與外部噪聲源的區(qū)別。誤差放大器決定LDO的PSRR,因而也決定了其抑制輸入端噪聲的能力。內(nèi)部噪聲則始終出現(xiàn)在LDO的輸出端。

圖1. 顯示內(nèi)部和外部噪聲源的簡化LDO框圖

內(nèi)部噪聲

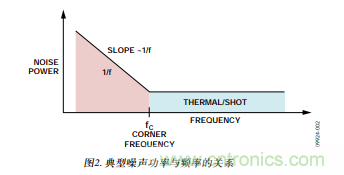

內(nèi)部噪聲有許多來源,各種噪聲源都有自己獨(dú)一無二的特性。圖2顯示了一個(gè)典型器件的噪聲如何隨頻率而變化,以及各類噪聲對總噪聲的貢獻(xiàn)。從1/f區(qū)到熱區(qū)的躍遷點(diǎn)稱為轉(zhuǎn)折頻率。內(nèi)部噪聲主要有以下幾類:熱噪聲、1/f噪聲、散粒噪聲、爆裂或爆米花噪聲。

圖2. 典型噪聲功率與頻率的關(guān)系

熱噪聲

在絕對零度以上的任何溫度,導(dǎo)體或半導(dǎo)體中的載流子(電子和空穴)會發(fā)生擾動,這就是熱噪聲(亦稱約翰遜噪聲或白噪聲)的來源。熱噪聲功率與溫度成比例。它具有隨機(jī)性,因而不隨頻率而變化。

熱噪聲是一個(gè)物理過程,可以通過下式計(jì)算:

其中:

k表示波爾茲曼常數(shù)(1.38−23 J/K)。

T表示絕對溫度(K = 273°C)。

R表示電阻(單位Ω)。

B表示觀察到噪聲的帶寬(單位Hz,電阻上測得的均方根電

壓也是進(jìn)行測量的帶寬的函數(shù))。

例如,一個(gè)100 kΩ電阻在1 MHz帶寬和室溫下給電路增加的

噪聲為:

1/f噪聲

1/f噪聲來源于半導(dǎo)體的表面缺陷。1/f噪聲功率與器件的偏置電流成正比,并且與頻率成反比,這一點(diǎn)與熱噪聲不同。即使頻率非常低,該反比特性也成立,然而,當(dāng)頻率高于數(shù)kHz時(shí),關(guān)系曲線幾乎是平坦的。1/f噪聲也稱為粉紅噪聲,因?yàn)槠錂?quán)重在頻譜的低端相對較高。

1/f噪聲主要取決于器件幾何形狀、器件類型和半導(dǎo)體材料,因此,要創(chuàng)建其數(shù)學(xué)模型極其困難,通常使用各種情況的經(jīng)驗(yàn)測試來表征和預(yù)測1/f噪聲。一般而言,具有埋入結(jié)的器件,如雙極性晶體管和JFET等,其1/f噪聲往往低于MOSFET等表面器件。

散粒噪聲

散粒噪聲發(fā)生在有勢壘的地方,例如PN結(jié)中。半導(dǎo)體器件中的電流具有量子特性,電流不是連續(xù)的。當(dāng)電荷載子、空穴和電子跨過勢壘時(shí),就會產(chǎn)生散粒噪聲。像熱噪聲一樣,散粒噪聲也是隨機(jī)的,不隨頻率而變化。

爆裂或爆米花噪聲

爆裂或爆米花噪聲是一種低頻噪聲,似乎與離子污染有關(guān)。爆米花噪聲表現(xiàn)為電路的偏置電流或輸出電壓突然發(fā)生偏移,這種偏移持續(xù)的時(shí)間很短,然后偏置電流或輸出電壓又突然返回其原始狀態(tài)。這種偏移是隨機(jī)的,但似乎與偏置電流成正比,與頻率的平方成反比(1/f2

)。

由于現(xiàn)代半導(dǎo)體工藝技術(shù)的潔凈度非常高,爆裂噪聲幾乎已經(jīng)被消除,不再是器件噪聲的一個(gè)主要因素。

外部噪聲

外部噪聲源遠(yuǎn)多于內(nèi)部噪聲源,包括以下幾類:

• 耦合到敏感電路中的電磁場。

• 導(dǎo)致壓電材料產(chǎn)生干擾交流電壓的機(jī)械沖擊或振動。

• 來自其他電路,通過電源或設(shè)計(jì)不佳的PCB布局布線傳導(dǎo)或輻射到電路中的噪聲。

電磁耦合

電磁場可以通過以下一種或多種方法在電路中感應(yīng)噪聲:輻射耦合、容性耦合、感性耦合和傳導(dǎo)耦合。通過適當(dāng)?shù)?/div>

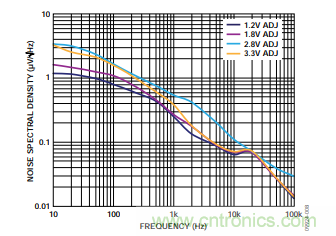

圖8. 噪聲譜密度與輸出電壓的關(guān)系(ADP223)

PCB布局布線和屏蔽技術(shù),可以降低此類耦合的影響,但

這不在本應(yīng)用筆記的討論范圍之內(nèi)。

壓電效應(yīng)

某些器件,如高容值多層陶瓷電容等,對機(jī)械沖擊和振動敏感(即具有顫噪效應(yīng)),這是因?yàn)槠浣Y(jié)構(gòu)中使用了高介電常數(shù)材料。這些電介質(zhì)具有高壓電性,很容易將微小的機(jī)械振動轉(zhuǎn)換為毫伏甚至微伏電平信號。因此,低電平信號鏈電路中不推薦使用高容值陶瓷電容。

雖然薄膜電容不具有壓電性,但它也對振動敏感,這是因?yàn)楸∧る娊橘|(zhì)上的任何機(jī)械應(yīng)力都會使薄膜厚度發(fā)生細(xì)微變化,導(dǎo)致電容略微增大或減小。電容中存儲的能量是恒定的,因此電壓必須略微改變以適應(yīng)電容變化。能量、電容和電壓之間的關(guān)系可通過下式來描述:

機(jī)械應(yīng)力消除后,電容上的電壓回到其原始狀態(tài)。如果機(jī)械應(yīng)力是周期性的,則將產(chǎn)生一個(gè)小交流電壓。

電源噪聲

電源噪聲和紋波一般是LDO輸出端僅次于內(nèi)部噪聲的最主要噪聲源。根據(jù)噪聲源的頻譜成分,LDO可以大大改善下游電路的電源質(zhì)量。

在許多系統(tǒng)中,來自交流電源或電池的電源由高效率開關(guān)模式電源轉(zhuǎn)換為中間電壓,以便在整個(gè)系統(tǒng)中分配。這些中間電壓在使用點(diǎn)被轉(zhuǎn)換為特定電壓。

開關(guān)模式電源的噪聲主要取決于其拓?fù)浣Y(jié)構(gòu)和負(fù)載狀態(tài)。頻譜成分可以是從數(shù)Hz到數(shù)十MHz。許多情況下,為了給敏感的模擬負(fù)載供電,需要通過LDO凈化高噪聲電源分配總線。LDO抑制輸入源噪聲的能力取決于其PSRR以及它如何隨頻率而變化。

LDO中的噪聲

LDO的主要內(nèi)部噪聲源是內(nèi)部基準(zhǔn)電壓和誤差放大器。現(xiàn)代LDO采用數(shù)十nA的內(nèi)部偏置電流工作,以便實(shí)現(xiàn)15 μA或更低的靜態(tài)電流。這種低偏置電流要求使用高達(dá)GΩ級的大值偏置電阻。

基準(zhǔn)電壓噪聲

電阻的熱噪聲定義為Vn = √(4kTRB),可以看出,電阻對基準(zhǔn)電壓電路噪聲的貢獻(xiàn)可能相當(dāng)大。幸運(yùn)的是,LDO的基準(zhǔn)電壓不需要數(shù)Hz以上的帶寬,可以利用片內(nèi)無源濾波來

輕松降低該噪聲。

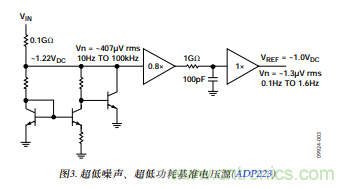

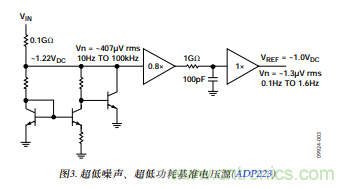

例如,一個(gè)源阻抗為0.1 GΩ的帶隙基準(zhǔn)電壓源在10 Hz到100kHz范圍內(nèi)具有407 μV rms的噪聲,將帶寬限制在10 Hz,噪聲可以降低至4.1 μV rms。如果將帶寬降低至1.6 Hz,則基準(zhǔn)電壓源的噪聲貢獻(xiàn)降低至1.3 μV rms。利用一個(gè)1 GΩ電阻和一個(gè)100 pF電容可以構(gòu)建一個(gè)轉(zhuǎn)折頻率為1.6 Hz的單極點(diǎn)RC濾波器。圖3顯示了如何在芯片中實(shí)現(xiàn)這樣一個(gè)1.0 V超低噪聲基準(zhǔn)電壓源。

誤差放大器噪聲

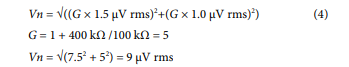

如果使用低噪聲基準(zhǔn)電壓源,則誤差放大器將成為總輸出噪聲的重要來源?;鶞?zhǔn)電壓源和誤差放大器的噪聲貢獻(xiàn)不相關(guān),必須通過均方根方法求和。

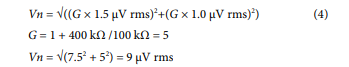

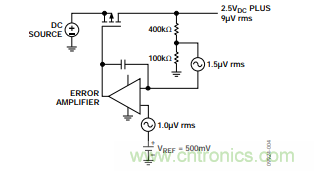

圖4所示為一個(gè)具有500 mV基準(zhǔn)電壓源的2.5 V輸出LDO示例。基準(zhǔn)電壓源的噪聲為1 μV rms,誤差放大器的噪聲為1.5μV rms,總噪聲為9 μV rms,計(jì)算如下:

圖4. 基準(zhǔn)電壓源和誤差放大器的噪聲貢獻(xiàn)(ADP223)

降低LDO噪聲

用于降低LDO噪聲的方法主要有兩種:

• 對基準(zhǔn)電壓進(jìn)行濾波

• 降低誤差放大器的噪聲增益

某些LDO允許使用外部電容來對基準(zhǔn)電壓進(jìn)行濾波。事實(shí)上,許多所謂的超低噪聲LDO都需要使用外部降噪電容來實(shí)現(xiàn)其低噪聲性能。對基準(zhǔn)電壓進(jìn)行外部濾波的缺點(diǎn)是啟動時(shí)間與濾波電容的大小成比例,圖3說明了為什么會如此。連接100 pF電容的節(jié)點(diǎn)被引出,以便連接外部電容。

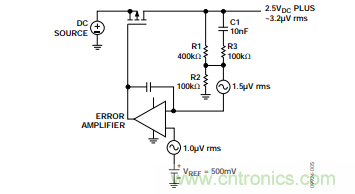

降低誤差放大器的噪聲增益對啟動時(shí)間的影響不如對基準(zhǔn)電壓進(jìn)行濾波那樣大,因而更容易在啟動時(shí)間與輸出噪聲之間權(quán)衡選擇。遺憾的是,對于固定輸出LDO,由于無法接入反饋節(jié)點(diǎn),輸出噪聲一般無法降低。然而,在大多數(shù)可調(diào)輸出LDO中,很容易接入反饋節(jié)點(diǎn)。

如果誤差放大器的噪聲貢獻(xiàn)大于基準(zhǔn)電壓源的貢獻(xiàn),則降低誤差放大器的噪聲增益可以顯著降低LDO的總噪聲。確定誤差放大器是否是主要噪聲來源的一種方法,就是比較特定LDO的固定輸出版本與可調(diào)輸出版本的噪聲。如果固定輸出LDO的噪聲遠(yuǎn)低于可調(diào)輸出LDO,則誤差放大器是主要噪聲源。

圖5所示為一個(gè)2.5 V輸出可調(diào)LDO,R1、R2、R3和C1為外部元件。所選的R3用于將放大器的高頻增益設(shè)置為1.5倍至2倍。某些LDO的相位裕量較低,或者在單位增益下不穩(wěn)定。所選的C1用于將降噪網(wǎng)絡(luò)(C1、R1和R3)的低頻零點(diǎn)設(shè)置在10 Hz至100 Hz范圍內(nèi),確保1/f區(qū)中的噪聲得到充分降低。

圖5. 降低可調(diào)輸出LDO的噪聲增益

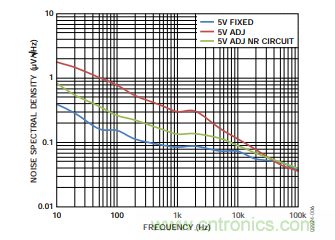

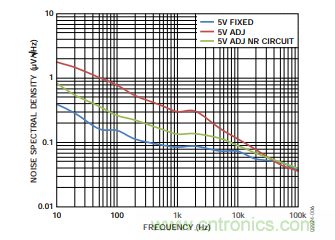

圖6顯示了降噪(NR)網(wǎng)絡(luò)對高壓可調(diào)LDO噪聲譜密度的影響。從圖6可以看出,在20 Hz至2 kHz范圍,噪聲性能提高大約3倍(~10 dB)。注意,兩條曲線在20 kHz以上融合,這

是因?yàn)檎`差放大器的閉環(huán)增益達(dá)到放大器的開環(huán)特性,無法進(jìn)一步降低噪聲增益。

在同一頻率范圍內(nèi),PSRR性能也有改善(更多信息參見“改善PSRR”部分)。

圖6. 可調(diào)輸出LDO的噪聲譜密度

LDO數(shù)據(jù)手冊中的噪聲規(guī)格

通常,LDO數(shù)據(jù)手冊通過兩種方式來規(guī)定內(nèi)部噪聲:

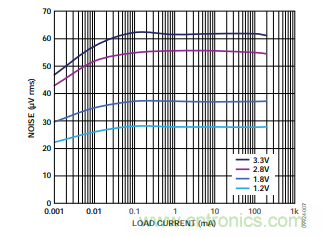

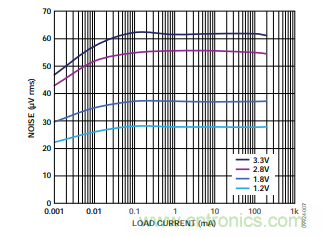

• 一定帶寬內(nèi)的總積分噪聲,用μV rms表示(見圖7)

• 噪聲譜密度曲線,噪聲與頻率的關(guān)系用μV/√Hz表示(見圖6)

ADI公司數(shù)據(jù)手冊規(guī)定10 Hz至100 kHz帶寬內(nèi)的總積分噪聲。圖7顯示了10 Hz至100 kHz帶寬內(nèi)ADP223在不同輸出電壓下的總均方根噪聲與負(fù)載電流的關(guān)系。

通常而言,輕負(fù)載下的均方根噪聲較低,因?yàn)長DO的帶寬隨著靜態(tài)電流而降低。當(dāng)負(fù)載電流達(dá)到數(shù)mA時(shí),LDO以全帶寬工作,噪聲不隨負(fù)載而變化。

圖7. 均方根噪聲與負(fù)載電流和輸出電壓的關(guān)系(ADP223)

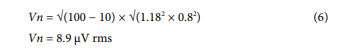

圖8所示為ADP223的噪聲譜密度圖,它顯示了10 Hz至100 kHz頻率范圍內(nèi)噪聲譜密度隨輸出電壓的變化情況。

在該帶寬內(nèi)對此圖中的數(shù)據(jù)進(jìn)行積分可得到均方根噪聲。對于任意頻率范圍,可以使用以下公式來估算均方根噪聲:

其中:

BW = NFU − NFL.

NFL為頻率下限時(shí)的噪聲(單位μV/√Hz)

NFU為頻率上限時(shí)的噪聲(單位μV/√Hz)

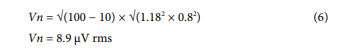

例如,對于圖8中的1.2 V輸出,10 Hz至100 Hz范圍內(nèi)的均方根噪聲約為:

噪聲譜密度測量在足夠高的負(fù)載電流下進(jìn)行,確保LDO以全帶寬工作,但又不能過高,以至于引起嚴(yán)重的自熱效應(yīng)。對于最大輸出電流為1 A或以下的大多數(shù)LDO,10 mA較為適當(dāng)。

圖8. 噪聲譜密度與輸出電壓的關(guān)系(ADP223)

比較LDO噪聲指標(biāo)

均方根噪聲用單一數(shù)值表示,因此它是用于比較不同LDO性能的一個(gè)有用指標(biāo)。然而,進(jìn)行比較的LDO的噪聲指標(biāo)必須是在相同的測試條件下測得。

例如,在10 Hz至100 kHz范圍內(nèi),1.2 V輸出的ADP223均方根噪聲約為27.7 μV rms。如果噪聲帶寬降到100 Hz至100kHz,則均方根噪聲降至約26.2 μV rms。均方根噪聲之所以降低,是因?yàn)檫M(jìn)行的噪聲測量不再包括10 Hz至100 Hz范圍內(nèi)的8.9 μV rms噪聲。

此外還必須留意所考慮的LDO的降噪特性。對于需要外部電容進(jìn)行降噪的LDO,不使用電容時(shí)的噪聲可能比使用電容時(shí)高100倍。在要求小尺寸和低成本的應(yīng)用中,出于節(jié)省PCB面積和成本考慮,可能會選擇不需要外部降噪電容,但噪聲略高于需要降噪電容的LDO。

LDO PSRR

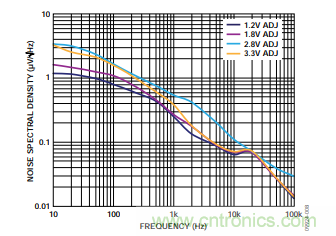

LDO的PSRR常常與內(nèi)部噪聲相混淆。簡單地說,PSRR衡量電路抑制電源輸入端出現(xiàn)的外來信號(噪聲和紋波),使這些干擾信號不致于破壞電路輸出的能力。電路的PSRR定義如下:

其中,VEIN和VEOUT分別是輸入端和輸出端出現(xiàn)的外來信號。

對于ADC、DAC和放大器等電路,該P(yáng)SRR適用于向目標(biāo)電路內(nèi)部供電的輸入端。對于LDO,輸入電源引腳為調(diào)節(jié)輸出電壓和內(nèi)部電路供電。

PSRR與頻率的關(guān)系

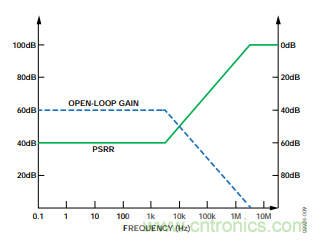

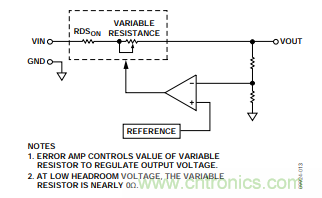

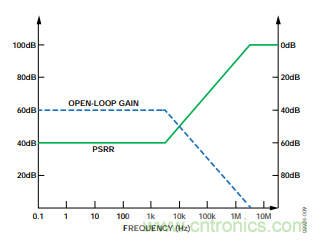

PSRR不是通過單一值來定義,因?yàn)樗c頻率相關(guān)。如圖1所示,LDO由基準(zhǔn)電壓、誤差放大器、MOSFET或雙極性晶體管等功率調(diào)整元件組成。誤差放大器提供直流增益以便調(diào)節(jié)輸出電壓。誤差放大器的交流增益特性在很大程度上決定了LDO的PSRR。典型LDO在10 Hz時(shí)可能具有高達(dá)80 dB的PSRR,但在數(shù)十kHz時(shí)則可能降至僅20 dB。

誤差放大器增益帶寬與PSRR的關(guān)系如圖9所示。本例已進(jìn)行高度簡化,輸出電容和調(diào)整元件寄生效應(yīng)被忽略。

PSRR等于60 dB開環(huán)增益的倒數(shù),直到3 kHz時(shí)增益開始滾降。PSRR以20 dB/10倍的速率降低,直到3 MHz時(shí)PSRR達(dá)到0 dB;對于此后所有更高的頻率,PSRR保持0 dB不變。

圖9. 簡化的LDO增益與PSRR的關(guān)系

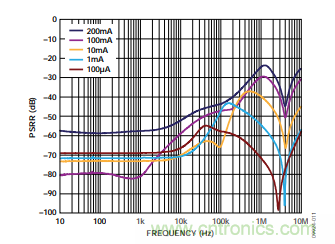

圖10的PSRR曲線顯示了表征LDO PSRR的三個(gè)主要頻域:基準(zhǔn)電壓PSRR區(qū)、開環(huán)增益區(qū)和輸出電容區(qū)。

圖10. 典型LDO PSRR與頻率的關(guān)系

基準(zhǔn)電壓PSRR區(qū)取決于基準(zhǔn)電壓放大器的PSRR和LDO開環(huán)增益。理想情況下,基準(zhǔn)電壓放大器完全不受電源擾動的影響。實(shí)際上,基準(zhǔn)電壓只需要抑制最高數(shù)十Hz的電源噪聲,因?yàn)檎`差放大器反饋確保在低頻時(shí)具有高PSRR。

在大約10 Hz以上的第二區(qū)中,PSRR主要由LDO的開環(huán)增益決定。此區(qū)中的PSRR是誤差放大器增益帶寬(最高為單位增益頻率)的函數(shù)。在低頻時(shí),誤差放大器的交流增益等于直流增益并保持不變,直至達(dá)到3 dB滾降頻率。在高于3dB滾降點(diǎn)的頻率,誤差放大器的交流增益隨著頻率提高而

降低,變化速率通常為20 dB/10倍。

在誤差放大器的單位增益頻率以上,控制環(huán)路的反饋對PSRR無影響,PSRR由輸出電容和輸入與輸出電壓之間的任何寄生效應(yīng)決定。在這些頻率,輸出電容ESR和ESL以及電路板布局布線會強(qiáng)烈影響PSRR。為了降低高頻諧振的影響,必須特別注意布局布線。

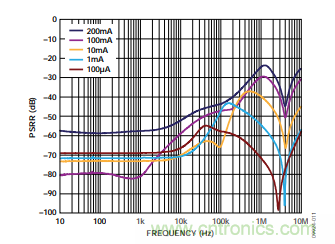

PSRR與負(fù)載電流的關(guān)系

如“PSRR與頻率的關(guān)系”部分所述,LDO的PSRR取決于誤差放大器反饋環(huán)路的增益帶寬,任何會影響此環(huán)路增益的因素都會影響LDO的PSRR。負(fù)載電流可以通過兩種方式影響PSRR。

在低負(fù)載電流下(通常小于50 mA),調(diào)整元件的輸出阻抗很高。由于控制環(huán)路的負(fù)反饋,LDO輸出似乎是理想的電流源。輸出電容和調(diào)整元件形成的極點(diǎn)導(dǎo)致輸出阻抗出現(xiàn)在相對較低的頻率,并且往往會提高低頻時(shí)的PSRR。低電流時(shí)輸出級的高直流增益往往也會提高誤差放大器單位增益

點(diǎn)以下頻率時(shí)的PSRR。

在重負(fù)載電流下,LDO輸出不太像是一個(gè)理想電流源,調(diào)整元件的輸出阻抗相對較低,導(dǎo)致輸出級的增益降低。輸出級增益的下降使得直流到反饋環(huán)路單位增益頻率范圍內(nèi)的PSRR降低。圖11顯示直流增益隨著負(fù)載電流的降低而顯著下降。從200 mA到100 mA,ADP151的直流增益下降超

過20 dB。

輸出級帶寬因?yàn)檩敵鰳O點(diǎn)頻率的提高而提高。在高頻時(shí),PSSR似乎應(yīng)當(dāng)隨著環(huán)路帶寬的提高而提高,但實(shí)際上,由于總環(huán)路增益的降低,高頻PSRR可能沒有提高。一般而言,輕負(fù)載時(shí)的PSRR優(yōu)于重負(fù)載時(shí)的PSRR。

圖11. 典型LDO PSRR與負(fù)載電流的關(guān)系(ADP151)

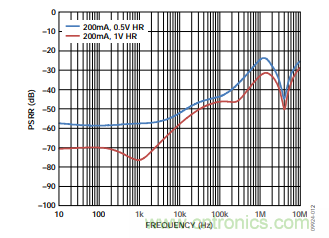

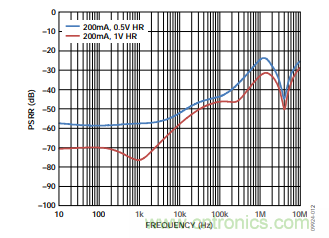

PSRR與LDO裕量的關(guān)系

LDO的PSRR也與輸入到輸出的壓差或裕量有關(guān)。對于固定裕量電壓,PSRR隨著負(fù)載電流的提高而降低,這在重負(fù)載電流和小裕量電壓時(shí)尤其明顯。圖12顯示了2.8 V輸出ADP151在200 mA負(fù)載、500 mV和1 V裕量下的PSRR差異。

隨著負(fù)載電流提高,調(diào)整元件(ADP151的P-MOSFET)脫離飽和狀態(tài),進(jìn)入三極工作區(qū),其增益相應(yīng)地降低,這導(dǎo)致LDO的總環(huán)路增益降低,因而PSRR下降。裕量越小,則增益降幅越大。在某些小裕量電壓,控制環(huán)路根本沒有增益,PSRR降至0。

降低環(huán)路增益的另一個(gè)因素是調(diào)整元件具有一個(gè)非零電阻,或稱RDSON。RDSON包括MOSFET導(dǎo)通電阻、片內(nèi)互連電阻和線焊電阻。RDSON通過LDO的壓差電壓估算。例如,WLCSP封裝的ADP151在200 mA負(fù)載下的最差情況壓差電壓為200 mV,這意味著RDSON約為1.0 Ω。圖13顯示了調(diào)整元件和RDSON的簡化原理圖。

圖12. 典型LDO PSRR與裕量的關(guān)系(ADP151)

負(fù)載電流引起的RDSON上的任何壓降都會導(dǎo)致調(diào)整元件有效部分的裕量降低相應(yīng)的量。例如,如果調(diào)整元件是一個(gè)1 Ω器件,負(fù)載電流為200 mA,則裕量將降低200 mV。當(dāng)LDO在1 V或更低的裕量電壓下工作時(shí),估算LDO PSRR時(shí)必須考慮此壓降。

改善PSRR

在既定的負(fù)載電流下,LDO的PSRR可以通過多種方式加以改善:

• 讓LDO在至少1 V的裕量下工作。某些LDO,如ADP151等,能夠在低至500 mV的裕量下很好地工作。

• 使用最大負(fù)載電流額定值至少比預(yù)期負(fù)載大1.5倍的LDO。

• 在LDO的輸入端或輸出端增加外部濾波。

• 如果裕量足夠,級聯(lián)兩個(gè)或更多LDO。

增加外部濾波以提高PSRR

增加外部濾波可以大大改善LDO電路的PSRR,但是,其代價(jià)是電路更復(fù)雜,并且裕量和效率會降低。根據(jù)應(yīng)用不同,可以將額外濾波添加到LDO的輸入端(前置濾波)或輸出端(后置濾波)。

后置濾波常常用于LDO輸出端存在顯著低頻噪聲的場合,如ADP151等現(xiàn)代低噪聲LDO不再需要后置濾波。后置濾波的缺點(diǎn)是濾波器電感的電阻會引起額外的負(fù)載調(diào)整誤差。

當(dāng)必須抑制高頻噪聲時(shí),如開關(guān)轉(zhuǎn)換器的輸出電壓紋波等,增加前置濾波更合適,而且它不會影響負(fù)載調(diào)整。

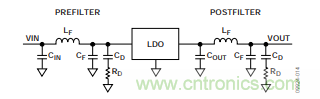

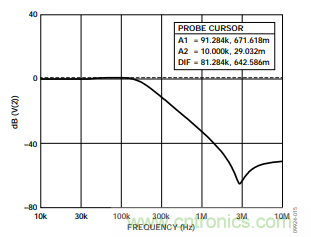

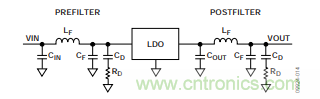

圖14顯示一個(gè)LDO電路同時(shí)采用前置濾波和后置濾波,然而,通常情況下僅使用一個(gè)外部濾波器。

圖14. 采用外部前置濾波和后置濾波的LDO

濾波器的主要元件是LF和CF,用于設(shè)置濾波器的轉(zhuǎn)折頻率。CD和RD消除LF和CF的諧振。CIN和COUT是用于LDO的典型輸入和輸出電容,但CIN不是必需的。

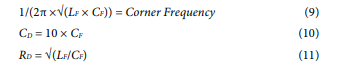

CF、LF、CD和RD的值可以通過以下方程式來確定:

例如,假設(shè)必須將一個(gè)開關(guān)轉(zhuǎn)換器的1 MHz紋波降低至少30 dB,100 kHz至200 kHz的轉(zhuǎn)折頻率應(yīng)當(dāng)足夠。

根據(jù)方程式9,假設(shè)CF= 1 μF、LF= 1 μH,則fC = 160 kHz。

根據(jù)方程式10,CD = 10 μF;根據(jù)方程式11,RD = 1 Ω。

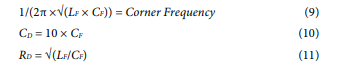

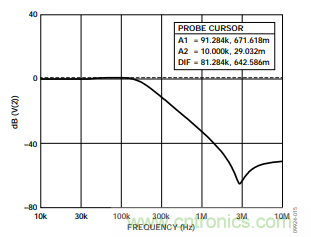

圖15顯示了示例濾波器的響應(yīng)。1 MHz時(shí)的衰減約為33 dB,最大峰化約為0.7 dB(81 kHz時(shí))。

電感LF的直流電阻應(yīng)盡可能低,以使裕量降幅最小(對于后置濾波器,則使負(fù)載調(diào)整誤差最小)。電感的飽和電流也必須至少像電路的最大預(yù)期負(fù)載電流一樣高。

圖15. 示例紋波濾波器的響應(yīng)

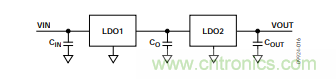

級聯(lián)多個(gè)LDO以提高PSRR

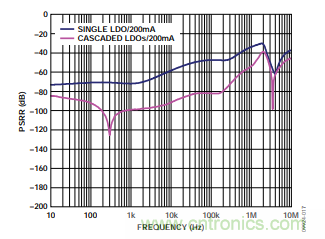

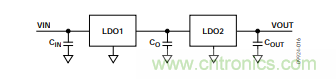

在裕量充足的應(yīng)用中,級聯(lián)多個(gè)LDO(如ADP151等)可以大大提高PSRR,同時(shí)保持ADP151的低輸出噪聲特性。圖16顯示兩個(gè)級聯(lián)LDO的原理圖。旁路電容CIN、COUT和CO等于ADP151數(shù)據(jù)手冊的推薦值,即1 μF。

圖16. 級聯(lián)LDO

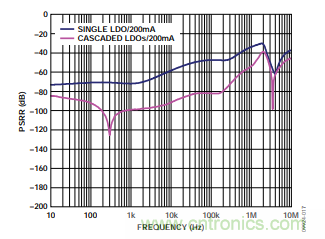

所選的LDO1輸出確保LDO2上的裕量至少為500 mV。為獲得最佳性能,LDO1上的裕量至少也應(yīng)為500 mV。圖17比較了一個(gè)1.8 V ADP151與兩個(gè)級聯(lián)ADP151的PSRR。兩種情況下的負(fù)載電流和裕量均分別為200 mA和1 V。從圖17可以清楚地看出,級聯(lián)兩個(gè)LDO可以將寬頻率范圍內(nèi)的

PSRR提高多達(dá)30 dB。

圖17. 一個(gè)LDO和級聯(lián)LDO的PSRR

比較LDO PSRR指標(biāo)

比較LDO的PSRR指標(biāo)時(shí),應(yīng)確保測量是在相同的測試條件下進(jìn)行。許多舊式LDO僅說明120 Hz或1 kHz時(shí)的PSRR,而未提及裕量電壓或負(fù)載電流。至少電氣技術(shù)規(guī)格表中的PSRR應(yīng)針對不同的頻率列出。為使比較有意義,最好應(yīng)使用不同負(fù)載和裕量電壓下的PSRR典型工作性能曲線。

輸出電容也會影響高頻時(shí)的LDO PSRR。例如,1 μF電容的阻抗是10 μF電容的10倍。在頻率高于誤差放大器的0 dB交越頻率時(shí),電源噪聲的衰減與輸出電容有關(guān),此時(shí)的容值特別重要。比較PSRR數(shù)值時(shí),輸出電容的類型和值必須相同,否則比較無效。

LDO總噪聲

內(nèi)部噪聲和PSRR均構(gòu)成LDO總輸出噪聲的一部分。根據(jù)應(yīng)用不同,內(nèi)部噪聲和PSRR二者之一的貢獻(xiàn)可能很重要,或者二者的貢獻(xiàn)均很重要。當(dāng)PSRR和內(nèi)生噪聲對應(yīng)用的整體性能均有影響時(shí),就無法應(yīng)用噪聲的單一數(shù)值。

一個(gè)典型應(yīng)用是利用開關(guān)轉(zhuǎn)換器為RF PLL供電。為了抑制來自開關(guān)轉(zhuǎn)換器的紋波,輸出通過一個(gè)LDO進(jìn)行調(diào)節(jié)。LDO的內(nèi)部噪聲會輕微調(diào)制PLL的電源,從而在PLL的輸出端引起相位噪聲。PLL的相位噪聲由VCO頻率偏移引起,與電源電壓有關(guān),表示為Δf/ΔV,常常稱為VCO的推移增益。

LDO的PSRR可以降低開關(guān)轉(zhuǎn)換器在LDO單位增益頻率以下的噪聲。超出LDO的單位增益頻率時(shí),開關(guān)轉(zhuǎn)換器噪聲由LDO輸出電容或LDO之后的無源濾波進(jìn)行衰減。未經(jīng)充分衰減的開關(guān)轉(zhuǎn)換器頻率諧波表現(xiàn)為PLL頻率任一端上的雜散。

結(jié)束語

一般而言,LDO噪聲包括兩部分:內(nèi)部或內(nèi)生噪聲以及外部或外生噪聲。

熱噪聲和1/f噪聲是主要的內(nèi)生噪聲源,與LDO的設(shè)計(jì)和半導(dǎo)體技術(shù)有關(guān)。

外部噪聲有許多來源,但最常見的是LDO輸入電源的噪聲。

由于LDO具有高增益以確保良好的線路和負(fù)載調(diào)整性能,因此它能夠衰減來自輸入電源的噪聲和紋波,這就是LDO的PSRR。LDO的帶寬有限,因此其PSRR隨著頻率提高而降低。LDO帶寬之外的噪聲無法通過LDO本身進(jìn)行衰減,可以利用無源濾波器來降低。

(來源:ADI,作者:Glenn Morita)

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進(jìn)行侵刪。