【導讀】當提到通信系統(tǒng)時,比起單端電路,差分電路總是能提供更加 優(yōu)良的性能。它們具有更高的線性度、抗共模干擾信號性能等。但是,對于差分電路還是有很多謎團。某些RF工程師認為很難設計、測試和調(diào)試它們。對于差分濾波器尤其如此。是時候揭開差分濾波器設計的神秘面紗了。

要做到這一點,我們要從通信系統(tǒng)接收鏈中的IF級濾波器開 始。我們將介紹基本濾波器的一些重要規(guī)格概念、幾類常用濾 波器的響應、切比雪夫1型濾波器應用,以及如何從單端濾波器 設計開始,然后將其轉(zhuǎn)化為差分濾波器設計。我們還將考察一 個差分濾波器設計示例,并討論有關如何優(yōu)化差分電路PCB設計的若干要點。

RF信號鏈應用中差分電路的優(yōu)點

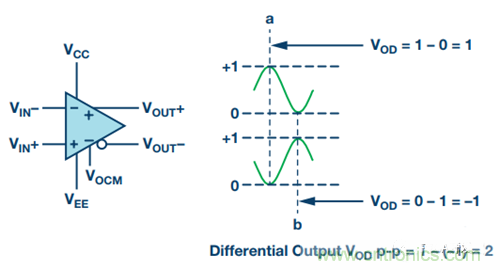

用戶利用差分電路可以達到比利用單端電路更高的信號幅度。 在相同電源電壓下,差分信號可提供兩倍于單端信號的幅度。 它還能提供更好的線性度和SNR性能。

圖1. 差分輸出振幅

差分電路對外部EMI和附近信號的串擾具有很好的抗擾性。這是 因為接收的有用信號電壓加倍,噪聲對緊密耦合走線的影響在 理論上是相同的,它們彼此抵消。

差分信號產(chǎn)生的EMI往往也較低。這是因為信號電平的變化(dV/ dt或dI/dt)產(chǎn)生相反的磁場,再次相互抵消。

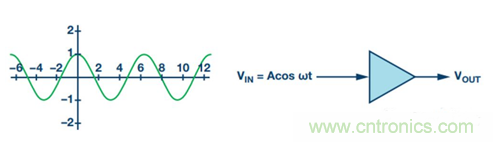

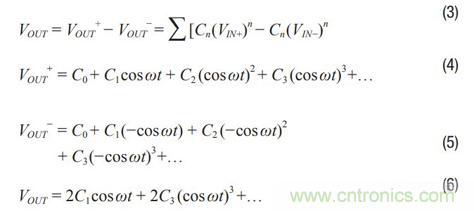

差分信號可抑制偶數(shù)階諧波。以下展示了連續(xù)波(CW)通過一個 增益模塊的示例。當使用一個單端放大器時,如圖2所示,輸出 可表示為公式1和公式2。

圖2. 單端放大器

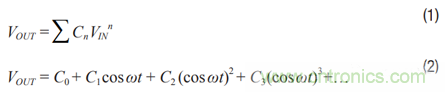

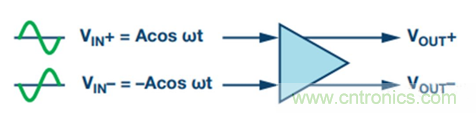

當使用一個差分放大器時,輸入和輸出如圖3所示,表示為公式 3、公式4、公式5和公式6。

圖3. 差分放大器

理想情況下,輸出沒有任何偶數(shù)階諧波,使得差分電路成為通信系統(tǒng)一個更好的選擇。

濾波器

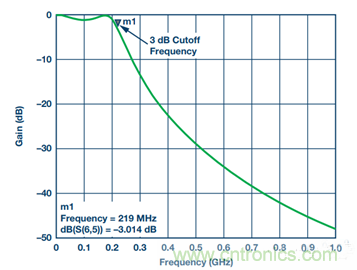

濾波器規(guī)格截止頻率、轉(zhuǎn)折頻率或拐點頻率是系統(tǒng)頻率響應的邊界,此時流經(jīng)系統(tǒng)的能量開始減少(衰減或反射),而不是自由通過。

圖4. 3 dB截止頻率點

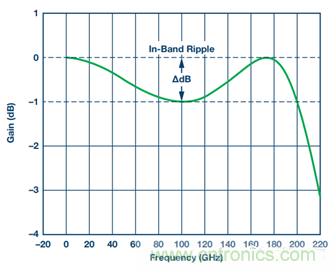

帶內(nèi)紋波指通帶內(nèi)插入損耗的波動。

圖5. 帶內(nèi)紋波

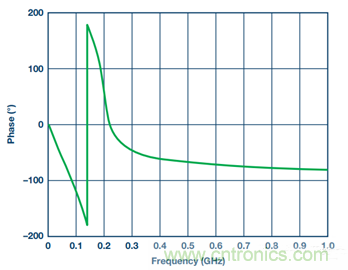

相位線性度指相移與目標頻率范圍內(nèi)的頻率成比例的程度。

圖6. 相位線性度

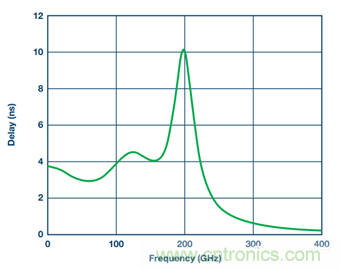

群延時衡量一個穿過受測器件的信號的各種正弦成分幅度包絡的時間延遲,它與各成分的頻率相關。

圖7. 群延時

濾波器比較

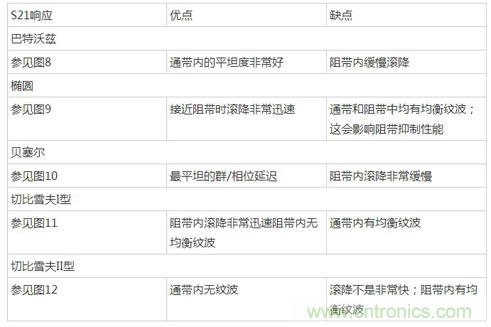

表1. 濾波器比較

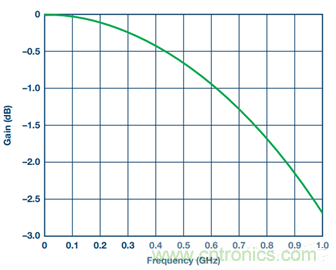

圖8. 巴特沃茲濾波器S21響應

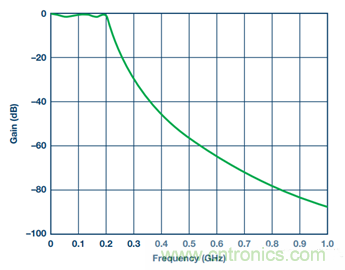

圖9. 橢圓濾波器S21響應

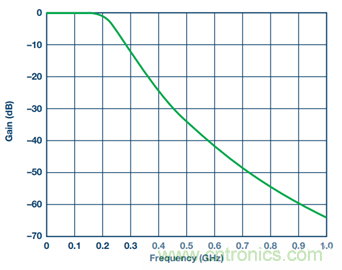

圖10. 貝塞爾濾波器S21響應。

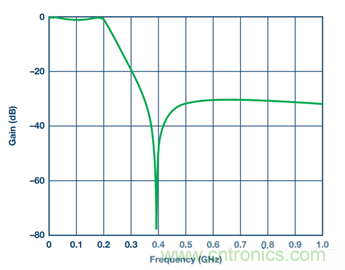

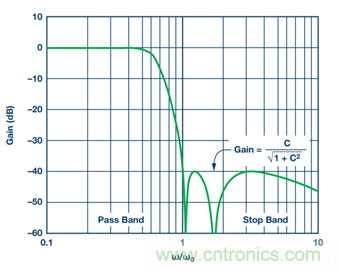

圖11. 切比雪夫I型濾波器S21響應

圖12. 切比雪夫II型濾波器S21響應

通信接收鏈中的IF濾波器基本上是低通濾波器或帶通濾波器。它用于抑制混疊信號以及有源器件產(chǎn)生的雜散。這些雜散包括諧波和IMD產(chǎn)物等。利用該濾波器,接收鏈可提供高SNR的信號供ADC分析。

切比雪夫I型濾波器具有良好的帶內(nèi)平坦度,阻帶內(nèi)滾降迅速且無均衡紋波響應,因而選擇它作為拓撲結構。

低通濾波器設計

由于接收機IF濾波器用于抑制雜散和混疊信號,因此阻帶滾降越快越好。但更快的滾降意味著要使用更高階器件。一般不推薦采用很高階的濾波器,原因如下:

在設計和調(diào)試階段調(diào)諧困難。

量產(chǎn)困難:電容間和電感間存在差異,會造成每塊PCB板上的濾波器難以具有相同的響應。

PCB尺寸較大。

一般使用七階或更低階的濾波器。同時,當器件的階數(shù)相同時,若能承受更大的帶內(nèi)紋波,則可以選用更快的阻帶滾降。

然后所需的響應通過指定選定頻率點需要的衰減來定義。

為了確定通帶中的最大紋波量,應使該規(guī)格等于系統(tǒng)要求的最大限值。這樣有助于獲得更快的阻帶滾降。

使用濾波器軟件,如MathCad,® MATLAB,® 或ADS來設計單端低通濾波器。

或者手動設計濾波器。Chris Bowick的RF電路設計提供了很有用 的指南。

為了確定過濾器的順序,通過濾波器的截止頻率將其分開使加入的頻率標準化。

例如,若要求帶內(nèi)紋波為0.1 dB,3 dB截止頻率為100 MHz。在 250 MHz時,要求抑制性能為28 dB,所以頻率比為2.5。三階低通 濾波器可滿足這一要求。如果濾波器的源阻抗為200 Ω,濾波器 的負載阻抗也是200 Ω,則RS/RL為1 — 使用電容作為第一元件。這樣用戶獲得歸一化的C1 = 1.433, L2 = 1.594, C3 = 1.433。如果fc為100 MHz,使用公式7和公式8獲得最終結果。

其中:

CSCALED為最終電容值。LSCALED為最終電感值。Cn為低通原型電容元件值。Ln為低通原型電感元件值。RL為最終負載電阻值。fc 為最終截止頻率。C1SCALED = 1.433/(2π × 100 × 106 × 200) = 11.4 pFL2SCALED = (1.594 × 200)/(2π × 100 × 106) = 507.4 nHC3SCALED = 11.4 pF

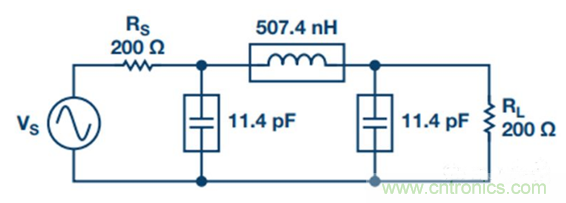

電路如圖13所示。

圖13. 單端濾波器示例

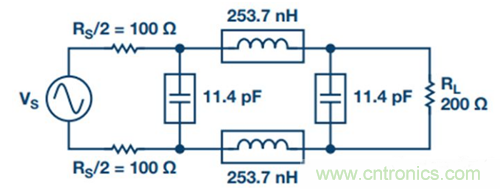

將單端濾波器轉(zhuǎn)化為差分濾波器(參見圖14)。

圖14. 單端濾波器轉(zhuǎn)化為差分濾波器

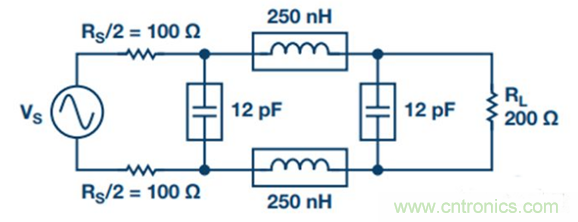

對各元件使用實際值,更新后的濾波器如圖15所示。

圖15. 最終差分濾波器

注意,如果混頻器或IF放大器的輸出阻抗以及ADC的輸入阻抗為容性,則考慮使用電容作為第一元件和最后元件會更好。另外,第一電容和最后電容的容值調(diào)諧速率(至少0.5 pF)必須高于混頻器或IF放大器的輸出阻抗以及ADC輸入阻抗的容值。否則,調(diào)諧濾波器響應將非常困難。

帶通濾波器設計

在通信系統(tǒng)中,當IF頻率相當高時,需要濾除某些低頻雜散,例如半IF雜散。為此需設計帶通濾波器。對于帶通濾波器,低頻抑制和高頻抑制不必對稱。設計帶通抗混疊濾波器的簡單方法是先設計一個低通濾波器,然后在濾波器最后一級的分流電容上并聯(lián)一個分流電感,用以限制低頻成分(分流電感是一個高通諧振極點)。如果一級高通電感還不夠,可在第一級分流電容上再并聯(lián)一個分流電感,從而更好地抑制低頻雜散。增加分流電感之后,再次調(diào)諧所有元件以獲得正確的帶外抑制規(guī)格,然后最終確定濾波器元件值。

注意,對于帶通濾波器,一般不建議使用串聯(lián)電容,因為這會增加調(diào)諧和調(diào)試的難度。電容值通常相當小,會受到寄生電容很大的影響。

應用示例

以下是ADL5201 和AD6641 間濾波器設計的示例。ADL5201是一款高性能IF數(shù)字控制增益放大器(DGA),針對基站實IF接收機應用或數(shù)字預失真(DPD)觀測路徑而設計。它具有30 dB增益控制范圍,線性度極高,OIP3達到50 dBm,電壓增益約為20 dB。 AD6641是 一款250 MHz帶寬DPD觀測接收機,集成一個12位500 MSPS ADC、一個16,000 × 12 FIFO和一個多模式后端,允許用戶通過串行端口檢索數(shù)據(jù)。該濾波器示例是一個DPD應用。

下面是取自一個實際通信系統(tǒng)設計的一些帶通濾波器規(guī)格:

中心頻率:368.4 MHz

帶寬:240 MHz

輸入和輸出阻抗:150Ω

帶內(nèi)紋波:0.2 dB

插入損耗:1 dB

帶外抑制:30 dB (614.4 MHz時)

要完成該示例設計:

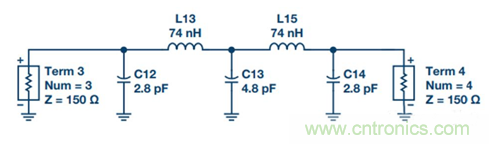

1. 從單端低通濾波器設計開始(參見圖16)。

圖16. 單端低通濾波器

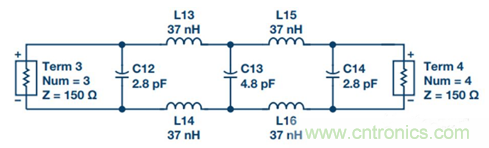

2. 將單端濾波器變?yōu)椴罘譃V波器。源阻抗和負載阻抗保持不變,所有電容并聯(lián),所有串聯(lián)電感減半并放在另一差分路徑中(參見圖17)。

圖17. 采用理想元件的差分低通濾波器

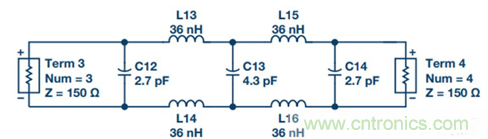

3. 用實際值優(yōu)化元件的理想值(參見圖18)。

圖18. 采用實際值的差分低通濾波器

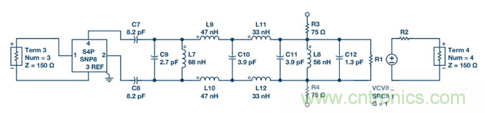

4. 對于子系統(tǒng)級仿真,應在輸入端增加ADL5201 DGA S參數(shù)文件,并使用壓控電壓源來模擬濾波器輸出端的 AD6641 ADC。為將低通濾波器變?yōu)閹V波器,增加兩個分流電感:L7與C9并聯(lián),L8與C11并聯(lián)。C12代表AD6641輸入電容。R3和R4是放在AD6641輸入端的兩個負載電阻,用作濾波器的負載。AD6641輸入為高阻抗。調(diào)諧后的情況參見圖19。

圖19. 差分帶通濾波器

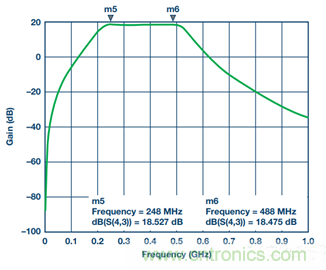

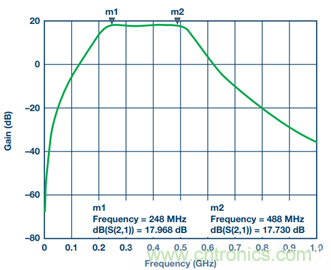

5. 采用理想元件的仿真結果如圖20所示。

圖20. 采用理想電感的濾波器傳輸響應

6. 用實際器件(例如Murata LQW18A)的電感S參數(shù)文件代替所有理想電感。插入損耗比使用理想電感略高。仿真結果略有變化,如圖21所示。

圖21. 采用Murata LQW18A電感的濾波器傳輸響應

差分濾波器布局考慮

成對差分走線的長度須相同。此規(guī)則源自這一事實:差分接收器檢測正負信號跨過彼此的點,即交越點。因此,信號須同時到達接收器才能正常工作。

差分對內(nèi)的走線布線須彼此靠近。如果一對中的相鄰線路之間的距離大于電介質(zhì)厚度的2倍,則其間的耦合會很小。此規(guī)則也是基于差分信號相等但相反這一事實,如果外部噪聲同等地干擾兩個信號,則其影響會互相抵消。同樣,如果走線并排布線,則差分信號在相鄰導線中引起的任何干擾噪聲都會被抵消。

同一差分對內(nèi)的走線間距在全長范圍內(nèi)須保持不變。如果差分走線彼此靠近布線,它們將影響總阻抗。如果此間距在驅(qū)動器與接收器之間變化不定,則一路上會存在阻抗不匹配,導致反射。

差分對之間的間距應較寬,以使其間的串擾最小。

如果在同一層上使用銅皮鋪地,應加大從差分走線到銅皮鋪地之間的間隙。推薦最小間隙為走線寬度的3倍。

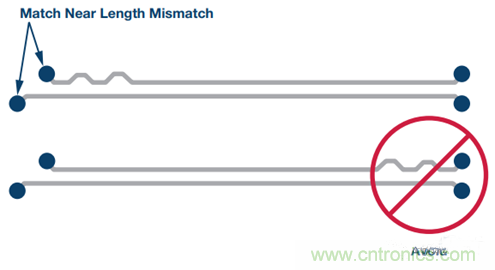

在靠近差分對內(nèi)偏斜源處引入少量彎彎曲曲的校正,從而降低 這種偏斜(參見圖22)。

圖22. 使用彎曲校正

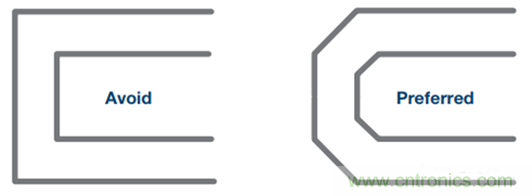

差分對布線時,應避免急轉(zhuǎn)彎(90°)(參見圖23)。

圖23. 避免90°彎曲

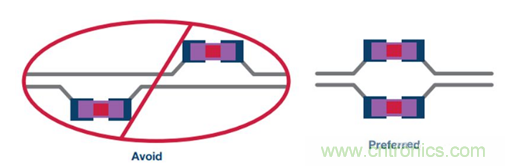

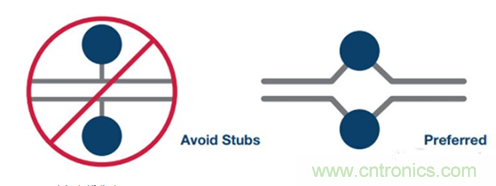

差分對布線時,應使用對稱布線(參見圖24)。若需要測試點, 應避免引入走線分支,而且測試點應對稱放置(參見圖25)。

圖24. 對稱布線指南

圖25. 避免走線分支

就降低對濾波器元件值的要求,減少印刷電路板(PCB)上的調(diào) 諧工作量而言,寄生電容和電感應盡可能小。與濾波器設計 中的電感設計值相比,寄生電感可能微不足道。寄生電容對 差分IF濾波器更為重要。IF濾波器設計中的電容只有幾pF。如 果寄生電容達到數(shù)十分之一pF,濾波器響應就會受到相當大的 影響。為了防止寄生電容影響,一個良好的做法是避免差分 布線區(qū)域和電源扼流圈下有任何接地或電源層。

ADI公司接收器參考設計板(參見圖26)提供了差分濾波器PCB布局 的一個示例。這顯示了ADL5201和AD6649之間有一個五階濾波 器。AD6649是一款14位250 MHz流水線式ADC,具有非常好的SNR 性能。

圖26. 差分電路PCB布局設計示例

更好地理解差分濾波器設計

差分電路可以為設計師提供一些重要優(yōu)勢?;蛟S使用差分電路最大的挑戰(zhàn)就是拋開它們難于設計、測試和校正的想法。一旦 您仔細觀察過如何使用差分濾波器后,您會發(fā)現(xiàn)自己正在使用 RF設計的重要新工具。